- 您现在的位置:买卖IC网 > Sheet目录1917 > DSPIC30F4011-30I/ML (Microchip Technology)IC DSPIC MCU/DSP 48K 44QFN

2010

Micr

och

ip

T

e

chn

o

logy

Inc.

DS70135G-pa

g

e

107

dsPIC30F401

1/4012

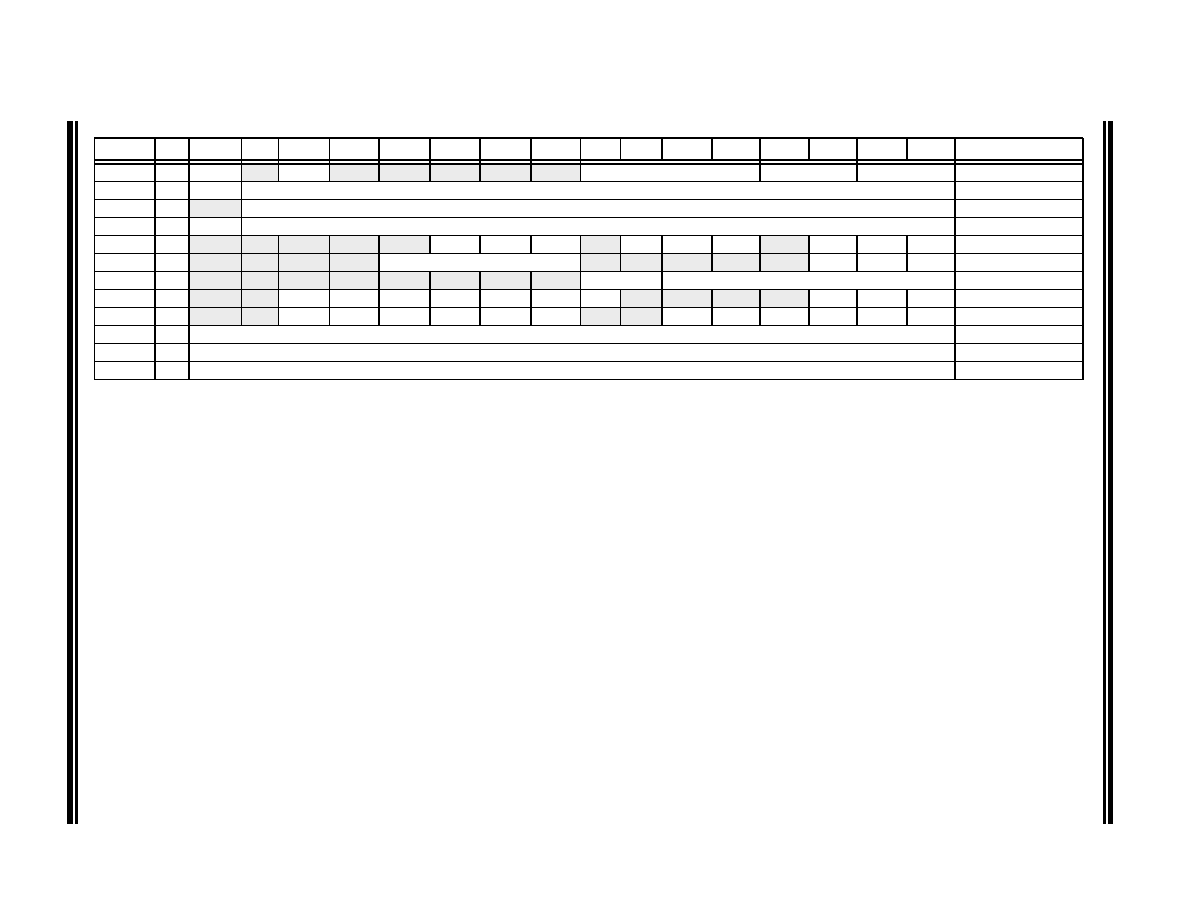

TABLE 15-1:

6-OUTPUT PWM REGISTER MAP(1)

SFR Name Addr.

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reset State

PTCON

01C0

PTEN

—PTSIDL

—

PTOPS<3:0>

PTCKPS<1:0>

PTMOD<1:0>

0000 0000 0000 0000

PTMR

01C2

PTDIR

PWM Timer Count Value

0000 0000 0000 0000

PTPER

01C4

—

PWM Time Base Period Register

0111 1111 1111 1111

SEVTCMP

01C6 SEVTDIR

PWM Special Event Compare Register

0000 0000 0000 0000

PWMCON1 01C8

—

PTMOD3 PTMOD2 PTMOD1

—

PEN3H

PEN2H

PEN1H

—PEN3L

PEN2L

PEN1L

0000 0000 1111 1111

PWMCON2 01CA

—

SEVOPS<3:0>

—

IUE

OSYNC

UDIS

0000 0000 0000 0000

DTCON1

01CC

—

DTAPS<1:0>

Dead-Time A Value

0000 0000 0000 0000

FLTACON

01D0

—

FAOV3H

FAOV3L

FAOV2H

FAOV2L

FAOV1H

FAOV1L FLTAM

—

FAEN3

FAEN2

FAEN1

0000 0000 0000 0000

OVDCON

01D4

—

POVD3H POVD3L POVD2H POVD2L POVD1H POVD1L

—

POUT3H POUT3L POUT2H POUT2L POUT1H POUT1L 1111 1111 0000 0000

PDC1

01D6

PWM Duty Cycle 1 Register

0000 0000 0000 0000

PDC2

01D8

PWM Duty Cycle 2 Register

0000 0000 0000 0000

PDC3

01DA

PWM Duty Cycle 3 Register

0000 0000 0000 0000

Legend:

— = unimplemented bit, read as ‘0’

Note

1:

Refer to the “dsPIC30F Family Reference Manual” (DS70046) for descriptions of register bit fields.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPIC30F4013-30I/ML

IC DSPIC MCU/DSP 48K 44QFN

DSPIC30F5013-30I/PT

IC DSPIC MCU/DSP 66K 80TQFP

DSPIC30F5015-30I/PT

IC DSPIC MCU/DSP 66K 64TQFP

DSPIC30F6010-20E/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6010A-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC30F6013A-30I/PF

IC DSPIC MCU/DSP 132K 80TQFP

DSPIC30F6014-30I/PF

IC DSPIC MCU/DSP 144K 80TQFP

DSPIC33EP512MU814-I/PL

IC DSC 16BIT 512KB 144LQFP

相关代理商/技术参数

DSPIC30F4011-30I/P

功能描述:数字信号处理器和控制器 - DSP, DSC 16bit Signal Cntrlr RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F4011-30I/PT

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 30M 48KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F4011T-20E/ML

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 44LD 20M 48KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F4011T-20E/PT

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 20M 48KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F4011T-20I/ML

功能描述:数字信号处理器和控制器 - DSP, DSC DIG SIG CONTR RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F4011T-20I/PT

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 20M 48KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F4011T-30I/ML

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 44LD 30M 48KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSPIC30F4011T-30I/PT

功能描述:数字信号处理器和控制器 - DSP, DSC 16 Bit MCU/DSP 30M 48KB FL RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT